## BrainScaleS Hands-On Tutorial —Overview—

S. Schmitt

E. Müller

Heidelberg University

NICE 2019 Albany CNSE Campus Albany, NY

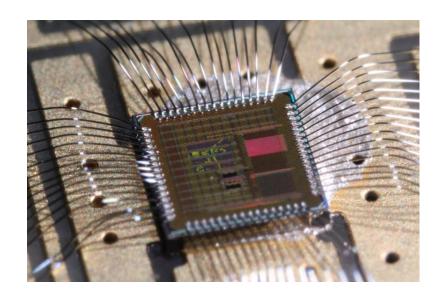

BrainScaleS-2 Prototype

BrainScaleS-1 Wafer Module

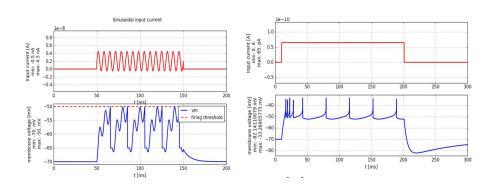

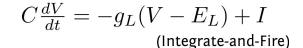

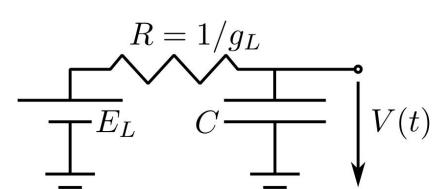

## BrainScaleS Architectures $C\frac{dV}{dt} = -g_L(V - E_L) + I + g_L\Delta_T \exp(\frac{V - V_T}{\Delta T}) - w$

$$C\frac{dV}{dt} = -g_L(V - E_L) + I + g_L \Delta_T \exp(\frac{V - V_T}{\Delta T}) - w$$

$$\tau_w \frac{dw}{dt} = a \left( V - E_L \right) - w$$

(Adaptive Exponential Integrate-and-Fire)

- Physical Model:

- an electronic circuit for each neuron and synapse

- Time models itself

- Accelerated dynamics: 1000 10000 faster wrt. biology

#### BrainScaleS-1

- Wafer scale neuromorphic experiments can be conducted via PyNN

- Networks described in terms of populations of neurons and their connections

- Low-level access to hardware parameters possible

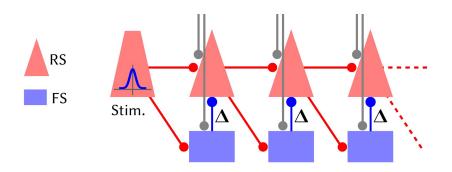

## Wafer-scale Synfire Chain

- Hardware Implementation similar to "Characterization and Compensation of Network-Level Anomalies in Mixed-Signal Neuromorphic Modeling Platforms" (Petrovici 2014)

- > 13k neurons and ~200k synapses

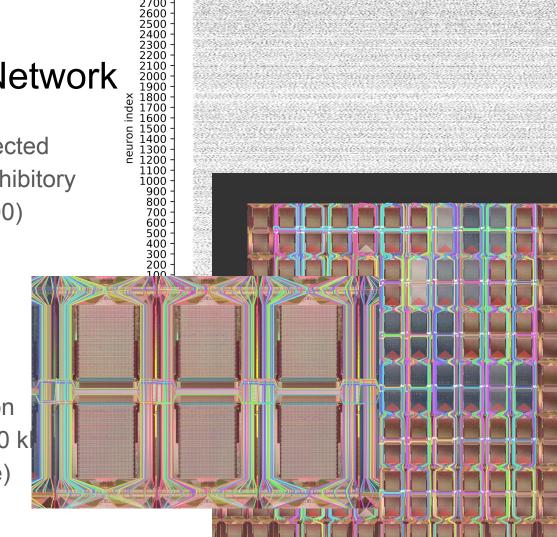

## (Balanced) Random Network

"Dynamics of Sparsely Connected Networks of Excitatory and Inhibitory Spiking Neurons" (Brunel 2000)

- 3000 neurons

- ~700k synapses

- 138 HICANN chips

- 800 individual external poisson sources with 50 Hz each -> 40 kl (bio) (400 MHz wall clock rate)

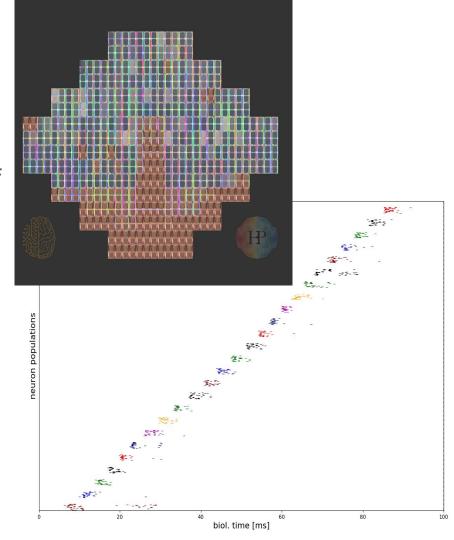

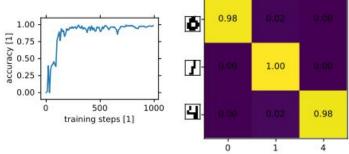

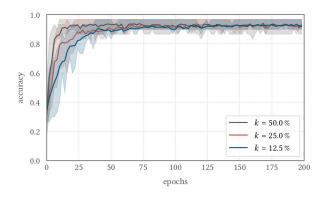

# Training deep networks with time-to-first-spike coding on the BrainScaleS wafer-scale system

- Hardware Implementation of "Supervised Learning Based on Temporal Coding in Spiking Neural Networks" (Mostafa 2018)

- Proof-of-concept implementation that learns to recognize patterns on the BrainScaleS using time-to-first-spike coding

- Single spikes promise to be an energy efficient and fast (~µs) approach to feature detection on neuromorphic hardware

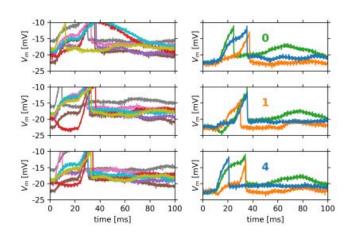

#### BrainScaleS-2

- Essentially all of BSS-1 (however: small prototype chip)

- Embedded processor for programmable plasticity

- observe: accumulated correlation, neuron spike counts, (individual spikes)

- o control: weights, neuron parameters, ...

- → two-factor + reward-modulated STDP,

structural plasticity, homeostasis, ...

- Embedded processor for other tasks:

- virtual environments; closed-loop sensor/motor modeling

- self-calibration

### BrainScaleS-2 Experiments

#### Examples:

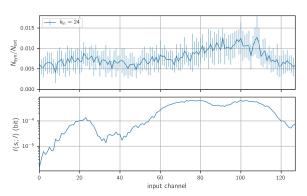

- Structural Plasticity

- e.g. auditory feature selection

- Closed-Loop

Reinforcement Learning

(https://doi.org/10.3389/fnins.2019.00260)

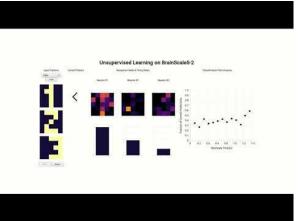

- Unsupervised learning,

e.g., using Spike-based

Expectation Maximization

### BrainScaleS-1: Hands-On

- You will remote access BrainScaleS-1 via a jupyter notebook

- You will define spiking neural networks using the Python-based PyNN API

- You will visualization the generated hardware configuration

- You will run experiments and analyse the results

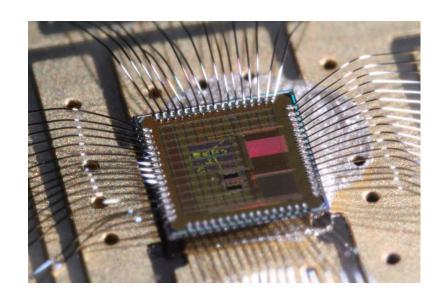

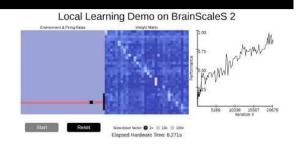

### BrainScaleS-2: Hands-On

- You will access one local "HICANN-DLS v2 Prototype"

- (we can also use some more setups remotely)

- You will work with the lowest configuration API level (exposing all bits and pieces)

- You will use the embedded processor