# Introducing Loihi

Mike Davies Director, Neuromorphic Computing Lab | Intel Labs

Acknowledgement to the entire Loihi team: Narayan Srinivasa, Tsung-Han Lin, Gautham Chinya, Yongqiang Cao, Sri Harsha Choday, Georgois Dimou, Prasad Joshi, Nabil Imam, Shweta Jain, Yuyun Liao, Chit-Kwan Lin, Andrew Lines, Ruokun Liu, Deepak Mathaikutty, Steve McCoy, Arnab Paul, Jon Tse, Guru Venkataramanan, Yi-Hsin Weng, Andreas Wild, Yoonseok Yang, and Hong Wang

# Motivation: The Case for Neuromorphic Computing

#### Problem Statement:

Emerging computing workloads demand intelligent behaviors that we do not know how to deliver efficiently with today's algorithms and computing architectures.

#### Examples:

- Online and lifelong learning

- Learning without cloud assistance

- Learning with sparse supervision

- Understanding spatiotemporal data

- Probabilistic inference and learning

- Sparse coding/optimization

- Nonlinear adaptive control

- Pattern matching with high occlusion

- SLAM and path planning

#### Potential Future Product Applications

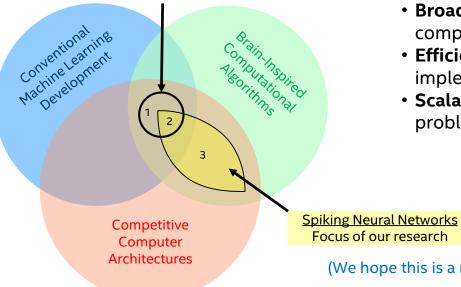

### Solution Exploration Space

"Deep Learning" / Artificial Neural Networks

#### **Research Goals:**

- Broad class of brain-inspired computation

- Efficient hardware implementations

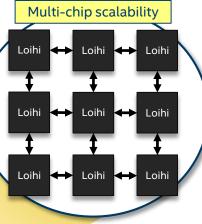

- Scalable from small to large problems and systems

Focus of our research

#### (We hope this is a non-empty class!)

# **The Engineering Perspective**

- Nature has come up with something amazing. Let's copy it...

- Not so simple very different design regimes

- Yet objectives and constraints are largely the same...

- Energy minimization

- Fast response time

- Cheap to produce

Need to understand and apply the basic principles, *adapting for differences*

#### Status today:

|                                  |                     | Nature                |                                     | Silicon                | Ratio              |

|----------------------------------|---------------------|-----------------------|-------------------------------------|------------------------|--------------------|

| Neuron density <sup>[1]</sup>    |                     | 100k/mm <sup>2</sup>  |                                     | 5k/mm <sup>2</sup>     | 20x                |

| Synaptic area <sup>[1]</sup>     |                     | 0.001 um <sup>2</sup> |                                     | 0.4 um <sup>2[2]</sup> | 400x               |

| Synaptic Op Energy               |                     | ~2 fJ                 |                                     | ~4 pJ                  | 2000x              |

| But                              |                     |                       |                                     | [1] Planar neoco       | ortex [2] ~5b SRAM |

| Max firing rate                  |                     | 100 Hz                |                                     | 1 GHz                  | 10,000,000x        |

| Synaptic error rate              |                     | 75%                   |                                     | 0%                     | $\infty$           |

|                                  |                     |                       |                                     |                        |                    |

| Nature                           |                     |                       | Silico                              | n                      |                    |

| Autonomous self-assembly         |                     |                       | Fabricated manufacturing            |                        |                    |

| Per-instance variability desired |                     |                       | Variability causes brittle failures |                        |                    |

| SIC plasticity over lifeti       |                     | time                  | Must support rapid reprogramming    |                        |                    |

| 5                                | rministic operation |                       | Deterministic operation desired     |                        |                    |

|                                  |                     |                       |                                     |                        |                    |

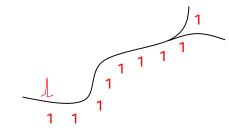

### Are Spiking Architectures Efficient?

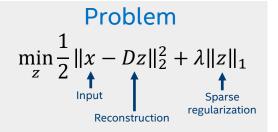

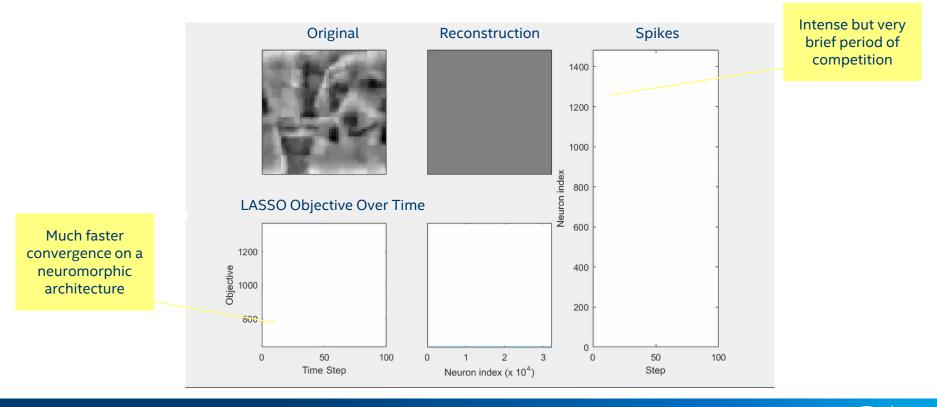

# One Compelling Example: LASSO Sparse Coding

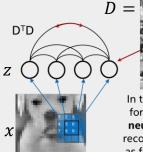

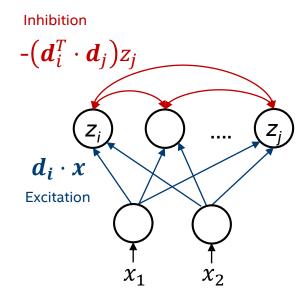

#### Implementation

In the neural network formulation, **feature neurons compete** to reconstruct image with as few contributors as possible

Tang et al, arxiv: 1705:05475

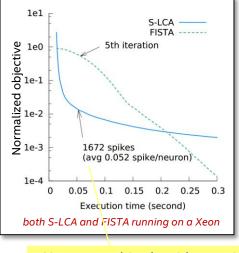

#### LASSO Optimization Using the Spiking Locally Competitive Algorithm

Neuromorphic algorithm rapidly finds a near-optimal solution

### Spiking LCA dynamics on a Loihi predecessor

### What this gives us... a baseline SNN architecture

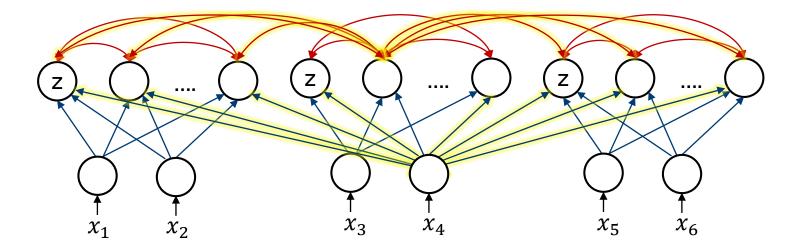

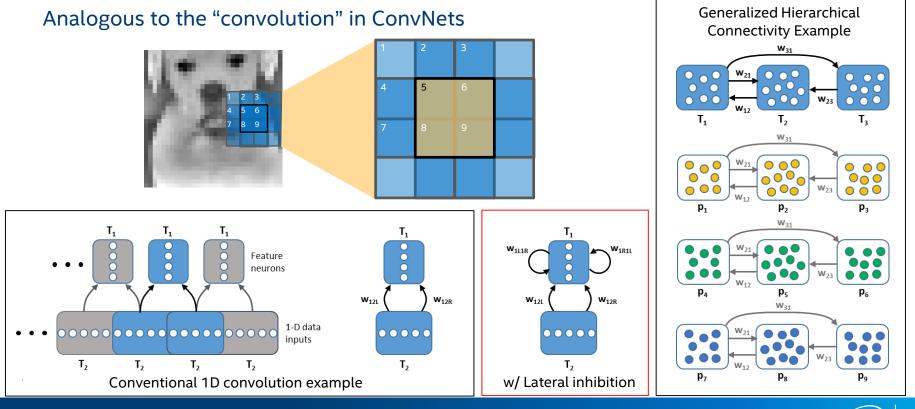

#### But how to scale to large LCA problems?

LCA is an all-to-all network...

Just 1000 feature neurons requires 1000<sup>2</sup> = 1M synapses

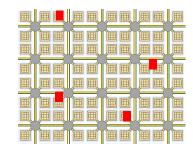

### Answer: Patch-based Connectivity Reuse

íntel

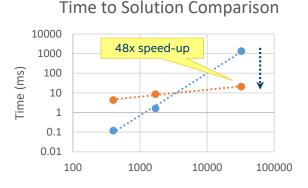

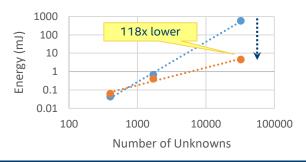

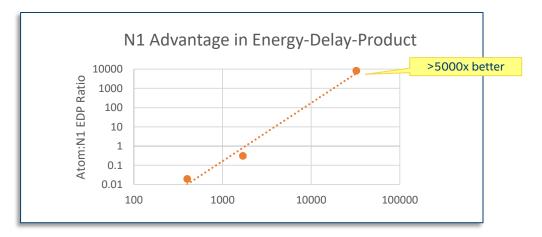

### Sparse Coding Results: N1 vs Atom CPU

**Energy to Solution Comparison**

# Comparison of sparse coding on N1 versus the FISTA\* LASSO solver on an Atom CPU\*\*

\* Best conventional LASSO solver (LARS also evaluated)

\*\* Iso-process, roughly iso-area (6-10mm<sup>2</sup>)

PTPX-based measurements

Atom (FISTA)

N1

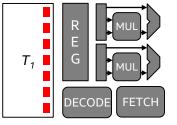

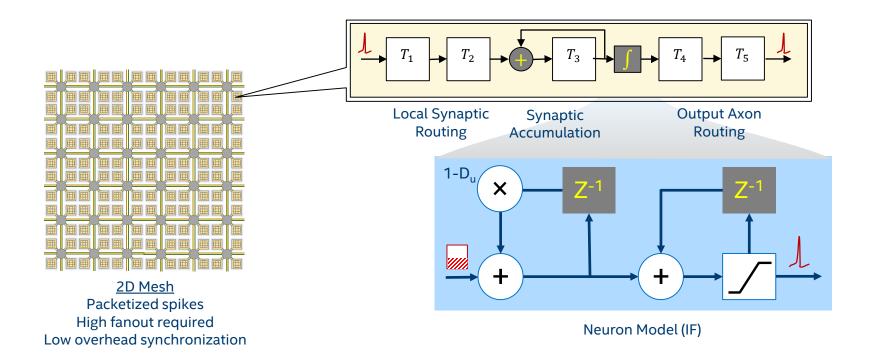

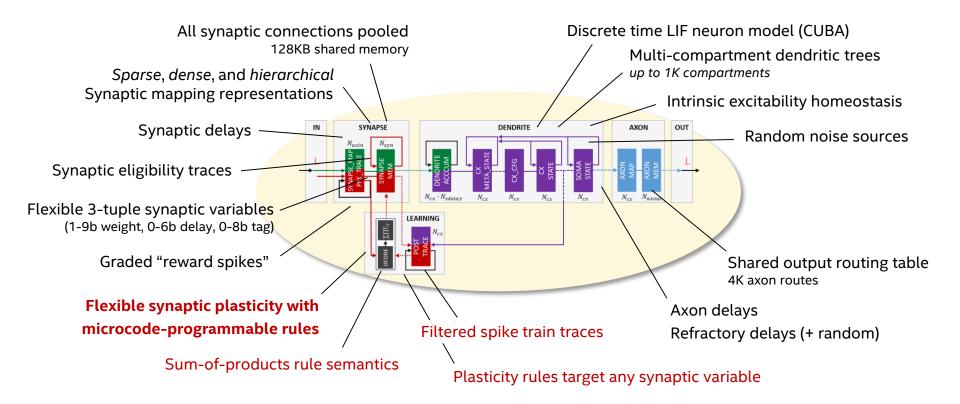

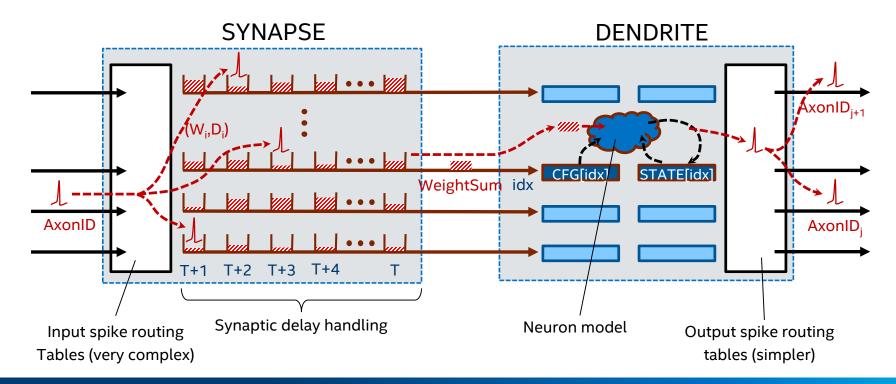

### Neuromorphic Core Architecture

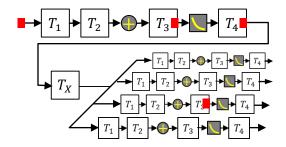

### **Basic Core Operation (Non-Learning)**

(Time multiplexing illustrated unrolled in space)

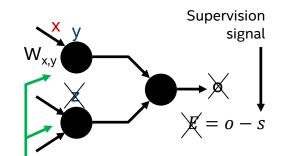

### Learning with Synaptic Plasticity

- Local learning rules essential property for efficient scalability Compatible with biological plausibility

- Should be derived by optimizing an emergent statistical objective Too much directionless experimentation otherwise

- Plasticity on **wide range of time scales** is needed Delayed reward/punishment responses, eligibility traces

Learning rules for weight  $W_{x,y}$ may *only* access presynaptic state x and postsynaptic state y

However *reward spikes* may be used to distribute graded reward/punishment values to a particular set of axon fanouts

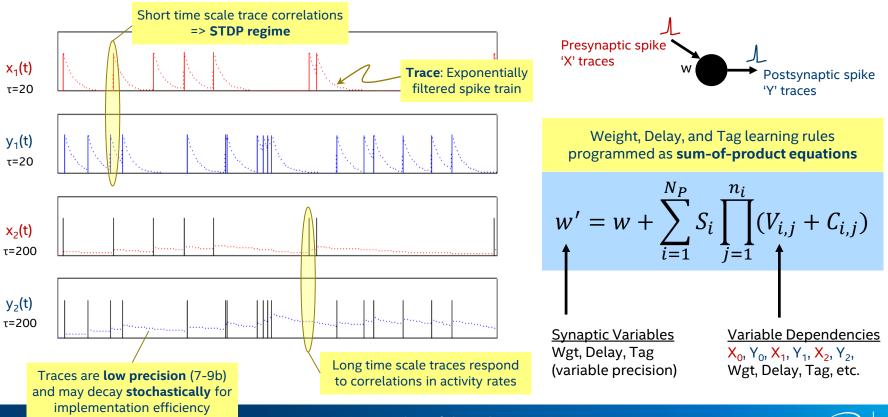

### Trace-Based Programmable Learning

### Learning Rule Examples

Pairwise STDP:

$$W(t+1) = W(t) - A_{-}x_{0}(t)y_{1}(t) + A_{+}x_{1}(t)y_{0}(t)$$

#### Triplet STDP with heterosynaptic decay:

$W(t+1) = W(t) - A_{-}x_{0}(t)y_{1}(t) + A_{+}x_{1}(t)y_{0}(t)y_{2}(t) - B \cdot W(t) \cdot y_{3}(t)$

**Delay STDP:**

$$D(t+1) = D(t) - A_{-} x_{0}(t)(127 - y_{1}(t)) + A_{+}(127 - x_{1}(t))y_{0}(t)$$

#### Two-variable Learning Rule Examples

Distal Reward with Synaptic Tags:

$$T(t+1) = T(t) - A_{-}x_{0}(t)y_{1}(t) + A_{+}x_{1}(t)y_{0}(t) - B \cdot T(t)$$

$$W(t+1) = W(t) + C \cdot r_1(t) \cdot T(t)$$

STDP with dynamic weight consolidation:

$W(t+1) = W(t) - A_{-}x_{0}(t)y_{1}(t) + A_{+}x_{1}(t)y_{0}(t)y_{2}(t) - B_{1}(W-T)y_{3}(t)y_{0}(t)$

$$T(t+1) = T(t) + \frac{1}{\tau_{cons}}(W-T) - B_2 T(w_{\theta} - T)(w_{max} - T)$$

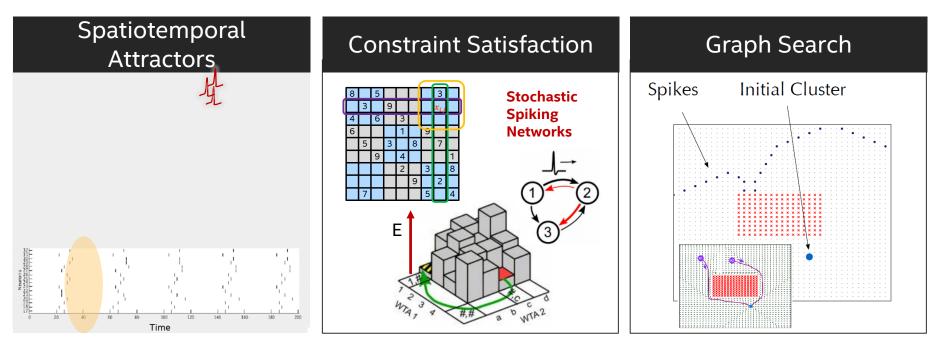

### Example Novel Algorithms Supported by Loihi

Artificial Olfaction

Sudoku

#### Path Planning

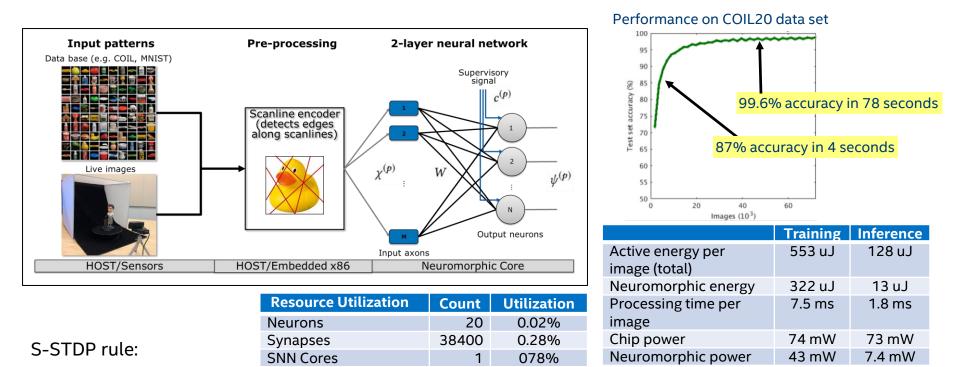

# Our "Hello World" Application: Supervised Learning for Object Recognition

$$W_{i,j}(t) = W_{i,j}(t-1) + \eta \cdot \left(u_{\kappa} \cdot \delta_{i,C(p)} - y_{i,0}\right) \cdot x_{j,1}$$

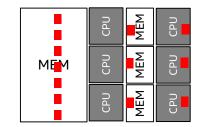

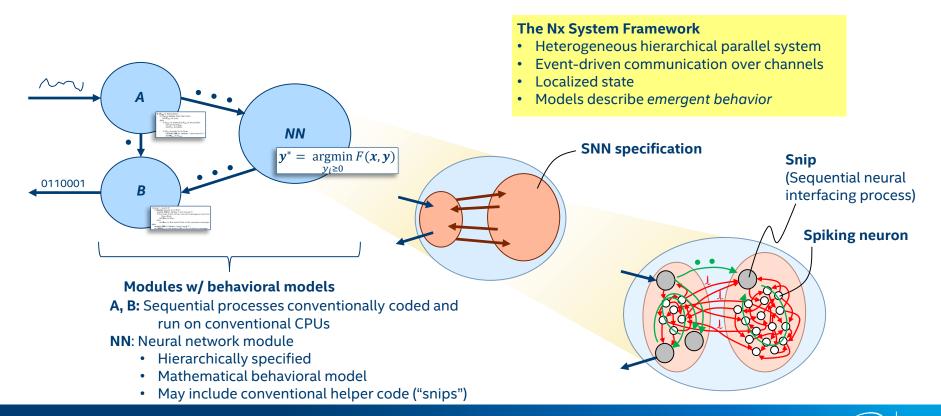

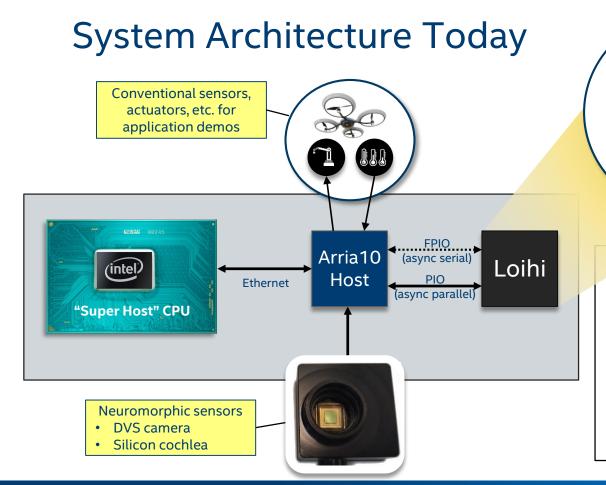

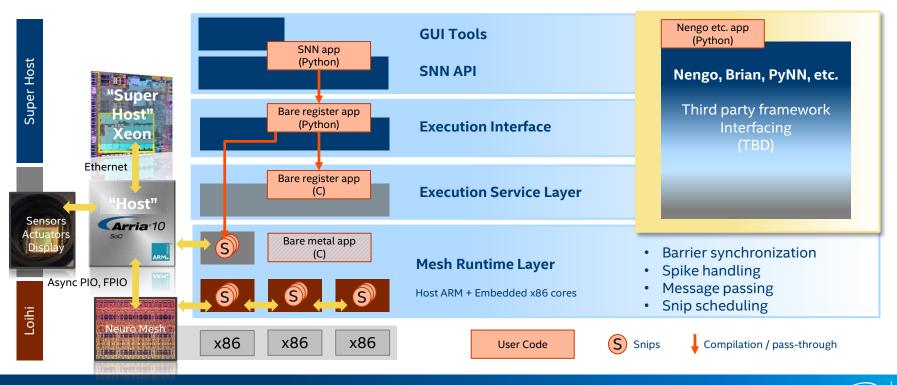

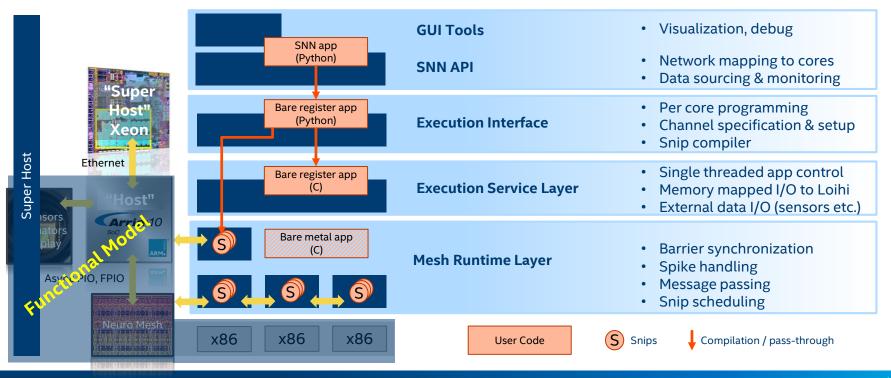

### Up to the 10,000 foot view

#### Mapping to the Physical Layer

**Abstraction Layer**

"Atoms" of the computational hierarchy are mapped to the system hardware resources

(Static scheduling)

**Physical Layer**

#### "Super Host" CPU

- Owns the high-level application

- Compilation, visualization, debug, UI

#### Arria10 Host

- Manages an entire mesh of Loihi chips

- Glue logic to Loihi interfaces

- Interface to real world/time data

- Spike encoding/decoding in some cases

#### Loihi

- Event-driven I/O model

- Participates in barrier synchronization

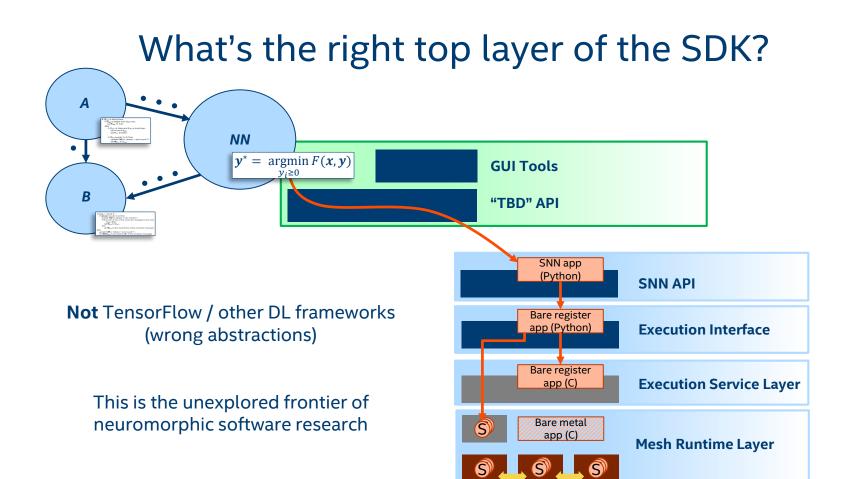

#### Current Software Development Kit (work in progress)

#### Current Software Development Kit (work in progress)

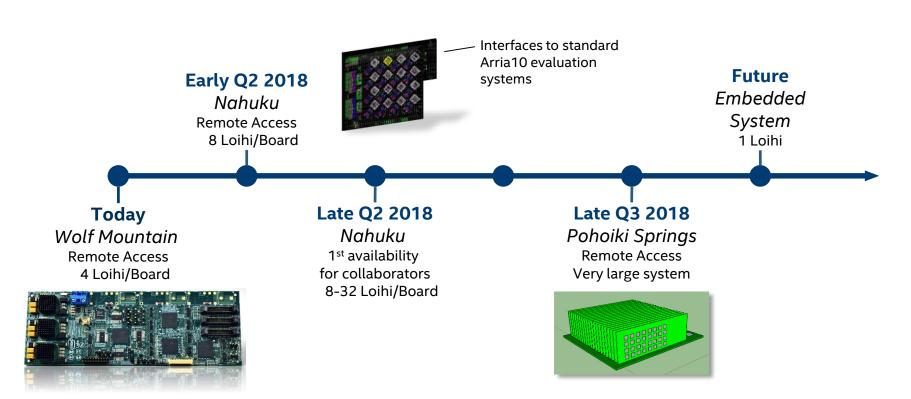

### Loihi Systems Outlook

# Intel Neuromorphic Research Community

#### **RV1: Theory**

- Abstract and quantify features of neuroscience to the context of systems engineering

- Computational complexity frameworks

#### **RV2: Algorithms**

• Principled derivations of SNN dynamics, features, and learning rules.

#### **RV5: Sensors and Control**

Sparse, event-driven I/O for SNN systems

Application Systems/SW Neuromorphic Algorithms Neuromorphic SDK

#### **RV3: Applications**

- Applications of Loihi and future Intel neuromorphic silicon / FPGA designs

- Benchmarks and value analysis may itself be research.

#### **RV4: Programming Models**

New paradigms for conceptualizing and specifying SNN/neuromorphic algorithms

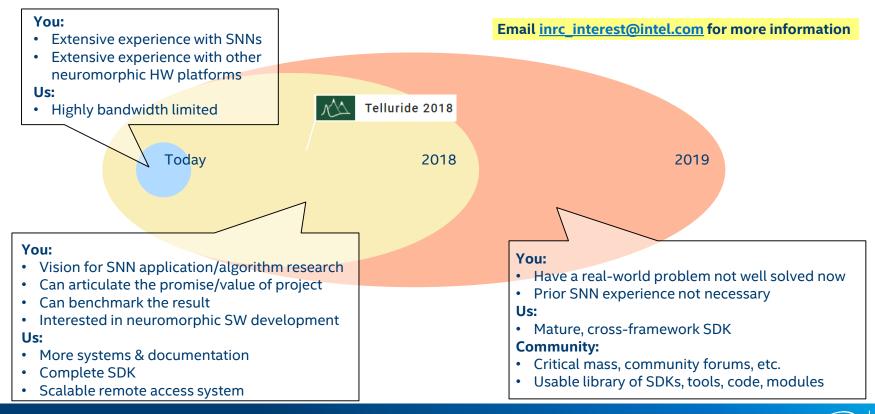

#### We wish to engage with collaborators in academic, government, industry research groups

#### **INRC** goals:

- Demonstrate value of Loihi vs conventional solutions

- Share code, results, algorithms

- Motivate improvements for future silicon iterations

#### What we offer to INRC collaborators

- Remote access to Loihi systems, SDK, SW

- Loaned Loihi systems and bare chips (limited)

- Opportunity for limited funding (RFP available late March)

### Please Join Us! (at the right time)

Email <u>inrc\_interest@intel.com</u> for more information

# **LEGAL INFORMATION**

This presentation contains the general insights and opinions of Intel Corporation ("Intel"). The information in this presentation is provided for information only and is not to be relied upon for any other purpose than educational. Statements in this document that refer to Intel's plans and expectations for the quarter, the year, and the future, are forward-looking statements that involve a number of risks and uncertainties. A detailed discussion of the factors that could affect Intel's results and plans is included in Intel's SEC filings, including the annual report on Form 10-K.

Any forecasts of goods and services needed for Intel's operations are provided for discussion purposes only. Intel will have no liability to make any purchase in connection with forecasts published in this document. Intel accepts no duty to update this presentation based on more current information. Intel is not liable for any damages, direct or indirect, consequential or otherwise, that may arise, directly or indirectly, from the use or misuse of the information in this presentation. Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at intel.com, or from the OEM or retailer.

Copyright © 2018 Intel Corporation. Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others